### **INTEGRATED CIRCUITS**

# DATA SHEET

For a complete data sheet, please also download:

- The IC04 LOCMOS HE4000B Logic Family Specifications HEF, HEC

- The IC04 LOCMOS HE4000B Logic Package Outlines/Information HEF, HEC

## HEF4022B MSI

4-stage divide-by-8 Johnson counter

Product specification

File under Integrated Circuits, IC04

January 1995

## 4-stage divide-by-8 Johnson counter

HEF4022B MSI

#### **DESCRIPTION**

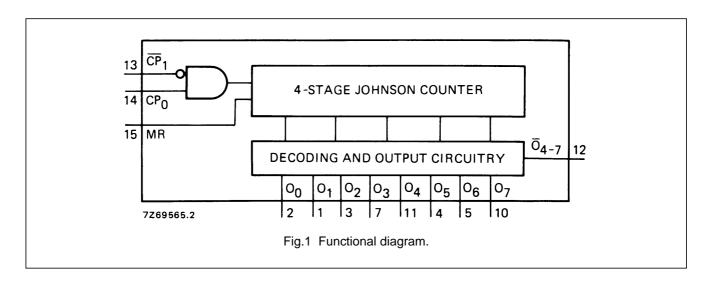

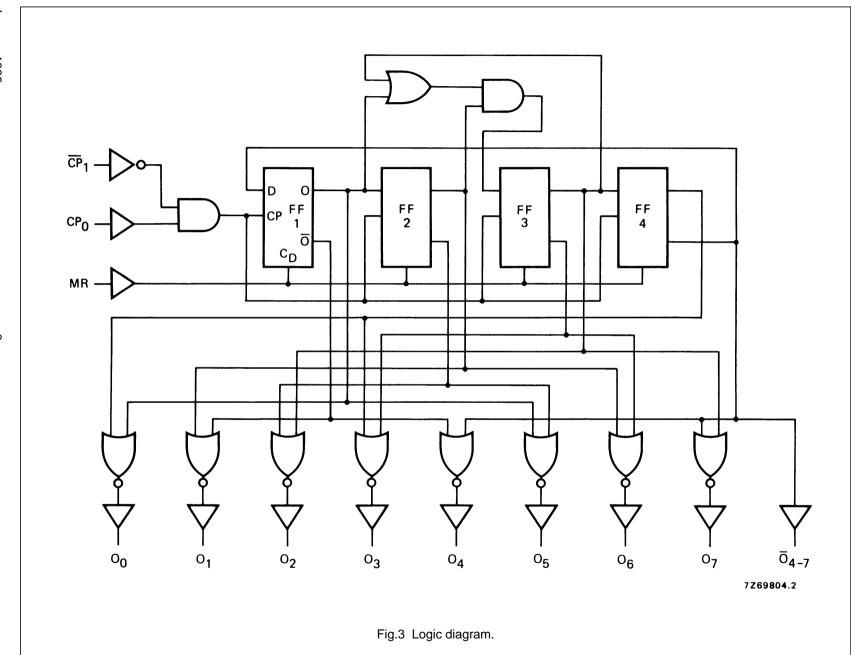

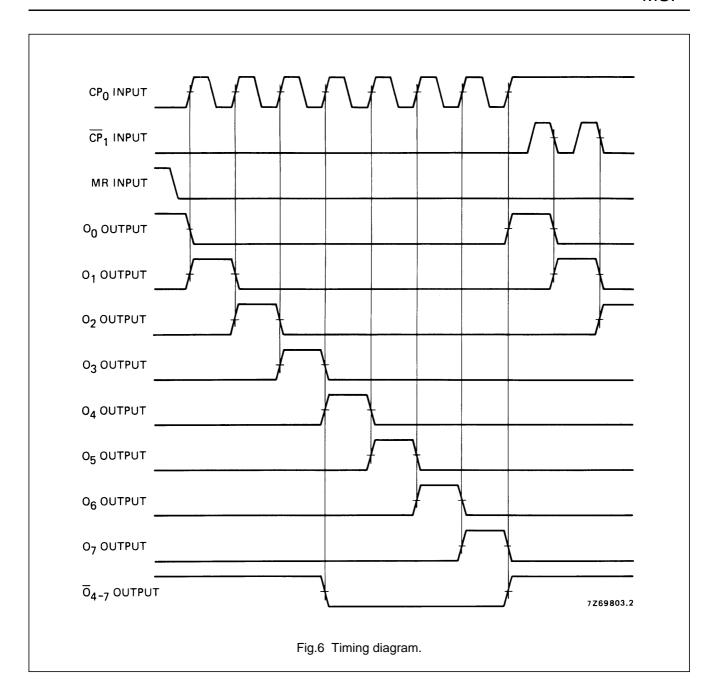

The HEF4022B is a 4-stage divide-by-8 Johnson counter with eight spike-free decoded active HIGH outputs ( $O_0$  to  $O_7$ ), an active LOW output from the most significant flip-flop  $(\overline{O}_{4-7})$ , active HIGH and active LOW clock inputs ( $CP_0$ ,  $\overline{CP}_1$ ) and an overriding asynchronous master reset input (MR).

The counter is advanced by either a LOW to HIGH transition at  $\overline{CP}_0$  while  $\overline{CP}_1$  is LOW or a HIGH to LOW transition at  $\overline{CP}_1$  while  $CP_0$  is HIGH (see also function table). Either  $CP_0$  or  $CP_1$  may be used as clock input to the

counter and the other clock input may be used as a clock enable input. When cascading counters, the  $\overline{O}_{4-7}$  output, which is LOW while the counter is in states, 4, 5, 6 and 7, can be used to drive the  $CP_0$  input of the next counter.

A HIGH on MR resets the counter to zero  $(O_0 = \overline{O}_{4-7} = \text{HIGH}; O_1 \text{ to } O_7 = \text{LOW})$  independent of the clock inputs  $(CP_0, \overline{CP}_1)$ .

Automatic code correction of the counter is provided by an internal circuit, following any illegal code the counter returns to a proper counting mode within 11 clock pulses.

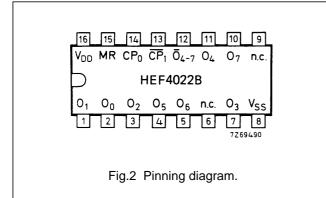

HEF4022BP(N): 16-lead DIL; plastic

(SOT38-1)

HEF4022BD(F): 16-lead DIL; ceramic (cerdip)

(SOT74)

HEF4022BT(D): 16-lead SO; plastic

(SOT109-1)

(): Package Designator North America

#### FAMILY DATA, IDD LIMITS category MSI

See Family Specifications

#### **PINNING**

CP<sub>O</sub> clock input (LOW to HIGH; edge-triggered)

CP<sub>1</sub> clock input (HIGH to LOW; edge-triggered)

$\begin{array}{ll} \text{MR} & \text{master reset input} \\ \text{O}_0 \text{ to O}_7 & \text{decoded outputs} \end{array}$

O<sub>4-7</sub> carry output (active LOW)

Philips Semiconductors

HEF4022B MSI

## 4-stage divide-by-8 Johnson counter

HEF4022B MSI

#### **FUNCTION TABLE**

| 1 |    | 0.0             | <del></del> | ODEDATION                                           |  |  |

|---|----|-----------------|-------------|-----------------------------------------------------|--|--|

|   | MR | CP <sub>0</sub> | CP₁         | OPERATION                                           |  |  |

|   | Н  | Х               | Х           | $O_0 = \overline{O}_{4-7} = H$ ; $O_1$ to $O_7 = L$ |  |  |

|   | L  | Н               | \           | Counter advances                                    |  |  |

|   | L  |                 | L           | Counter advances                                    |  |  |

|   | L  | L               | X           | No change                                           |  |  |

|   | L  | X               | Н           | No change                                           |  |  |

|   | L  | Н               |             | No change                                           |  |  |

|   | L  | \               | L           | No change                                           |  |  |

#### **Notes**

H = HIGH state (the more positive voltage)

L = LOW state (the less positive voltage)

X = state is immaterial

¬ = negative-going transition

#### **AC CHARACTERISTICS**

$V_{SS}$  = 0 V;  $T_{amb}$  = 25 °C;  $C_L$  = 50 pF; input transition times  $\leq$  20 ns

|                                                        | V <sub>DD</sub><br>V | SYMBOL           | MIN. | TYP. | MAX. |    | TYPICAL EXTRAPOLATION FORMULA        |

|--------------------------------------------------------|----------------------|------------------|------|------|------|----|--------------------------------------|

| Propagation delays                                     |                      |                  |      |      |      |    |                                      |

| $CP_0, \overline{CP}_1 \rightarrow O_n$                | 5                    |                  |      | 195  | 390  | ns | 168 ns + (0,55 ns/pF) C <sub>L</sub> |

| HIGH to LOW                                            | 10                   | t <sub>PHL</sub> |      | 75   | 145  | ns | 64 ns + (0,23 ns/pF) C <sub>L</sub>  |

|                                                        | 15                   |                  |      | 50   | 100  | ns | 42 ns + (0,16 ns/pF) C <sub>L</sub>  |

|                                                        | 5                    |                  |      | 245  | 485  | ns | 218 ns + (0,55 ns/pF) C <sub>L</sub> |

| LOW to HIGH                                            | 10                   | t <sub>PLH</sub> |      | 95   | 195  | ns | 84 ns + (0,23 ns/pF) $C_L$           |

|                                                        | 15                   |                  |      | 60   | 125  | ns | 52 ns + (0,16 ns/pF) C <sub>L</sub>  |

| $CP_0, \overline{CP}_1 \rightarrow \overline{O}_{4-7}$ | 5                    |                  |      | 245  | 485  | ns | 218 ns + (0,55 ns/pF) C <sub>L</sub> |

| HIGH to LOW                                            | 10                   | t <sub>PHL</sub> |      | 90   | 185  | ns | 79 ns + (0,23 ns/pF) C <sub>L</sub>  |

|                                                        | 15                   |                  |      | 60   | 120  | ns | 52 ns $+$ (0,16 ns/pF) $C_L$         |

|                                                        | 5                    |                  |      | 190  | 380  | ns | 163 ns + (0,55 ns/pF) C <sub>L</sub> |

| LOW to HIGH                                            | 10                   | t <sub>PLH</sub> |      | 75   | 145  | ns | 64 ns + (0,23 ns/pF) C <sub>L</sub>  |

|                                                        | 15                   |                  |      | 50   | 105  | ns | 42 ns $+$ (0,16 ns/pF) $C_L$         |

| $MR \rightarrow O_1 \text{ to } O_7$                   | 5                    |                  |      | 130  | 260  | ns | 103 ns + (0,55 ns/pF) C <sub>L</sub> |

| HIGH to LOW                                            | 10                   | t <sub>PHL</sub> |      | 55   | 105  | ns | 44 ns $+$ (0,23 ns/pF) $C_L$         |

|                                                        | 15                   |                  |      | 40   | 75   | ns | 32 ns + (0,16 ns/pF) $C_L$           |

| $MR \rightarrow O_0$                                   | 5                    |                  |      | 130  | 260  | ns | 103 ns + (0,55 ns/pF) C <sub>L</sub> |

| LOW to HIGH                                            | 10                   | t <sub>PLH</sub> |      | 55   | 105  | ns | 44 ns + (0,23 ns/pF) C <sub>L</sub>  |

|                                                        | 15                   |                  |      | 40   | 75   | ns | 32 ns + (0,16 ns/pF) C <sub>L</sub>  |

| $MR \rightarrow \overline{O}_{4-7}$                    | 5                    |                  |      | 110  | 220  | ns | 83 ns $+$ (0,55 ns/pF) $C_L$         |

| LOW to HIGH                                            | 10                   | t <sub>PLH</sub> |      | 45   | 90   | ns | 34 ns + (0,23 ns/pF) C <sub>L</sub>  |

|                                                        | 15                   |                  |      | 35   | 70   | ns | 27 ns + (0,16 ns/pF) $C_L$           |

| Output transition times                                | 5                    |                  |      | 60   | 120  | ns | 10 ns + (1,0 ns/pF) C <sub>L</sub>   |

| HIGH to LOW                                            | 10                   | t <sub>THL</sub> |      | 30   | 60   | ns | 9 ns $+$ (0,42 ns/pF) $C_L$          |

|                                                        | 15                   |                  |      | 20   | 40   | ns | 6 ns $+$ (0,28 ns/pF) $C_L$          |

|                                                        | 5                    |                  |      | 60   | 120  | ns | 10 ns + (1,0 ns/pF) C <sub>L</sub>   |

| LOW to HIGH                                            | 10                   | t <sub>TLH</sub> |      | 30   | 60   | ns | 9 ns $+$ (0,42 ns/pF) $C_L$          |

|                                                        | 15                   |                  |      | 20   | 40   | ns | 6 ns $+$ (0,28 ns/pF) $C_L$          |

## 4-stage divide-by-8 Johnson counter

HEF4022B MSI

#### **AC CHARACTERISTICS**

$V_{SS}$  = 0 V;  $T_{amb}$  = 25 °C;  $C_L$  = 50 pF; input transition times  $\leq$  20 ns

|                                    | V <sub>DD</sub><br>V | SYMBOL            | MIN. | TYP. | MAX. |                    |

|------------------------------------|----------------------|-------------------|------|------|------|--------------------|

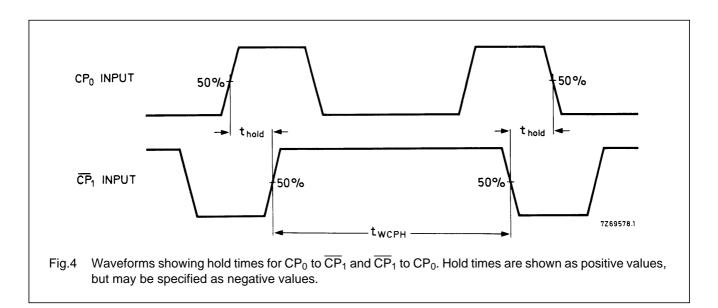

| Hold times                         | 5                    |                   | 140  | 70   | ns   |                    |

| $CP_0 \rightarrow \overline{CP}_1$ | 10                   | t <sub>hold</sub> | 50   | 25   | ns   |                    |

|                                    | 15                   |                   | 30   | 15   | ns   |                    |

|                                    | 5                    |                   | 170  | 85   | ns   |                    |

| $\overline{CP}_1 \rightarrow CP_0$ | 10                   | t <sub>hold</sub> | 60   | 30   | ns   |                    |

|                                    | 15                   |                   | 40   | 20   | ns   |                    |

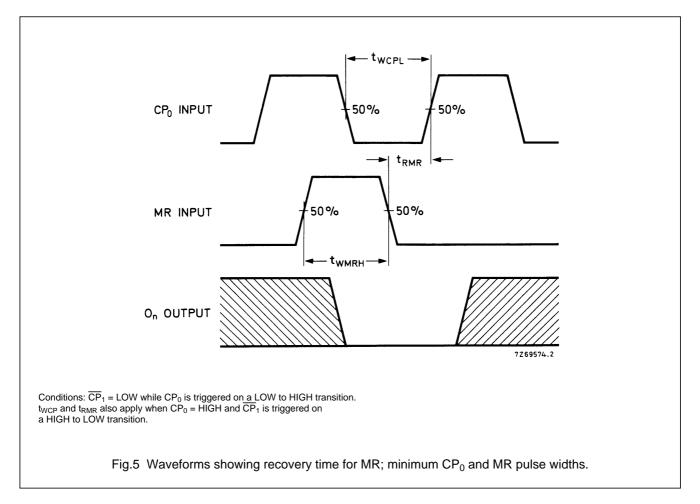

| Minimum clock                      | 5                    |                   | 75   | 35   | ns   |                    |

| pulse width                        | 10                   | t <sub>WCP</sub>  | 30   | 15   | ns   |                    |

|                                    | 15                   |                   | 20   | 10   | ns   | see also waveforms |

| Minimum MR                         | 5                    |                   | 70   | 35   | ns   | Figs 4 and 5       |

| pulse width; HIGH                  | 10                   | t <sub>WMRH</sub> | 30   | 15   | ns   |                    |

|                                    | 15                   |                   | 20   | 10   | ns   |                    |

| Recovery time                      | 5                    |                   | 30   | 10   | ns   |                    |

| for MR                             | 10                   | t <sub>RMR</sub>  | 15   | 5    | ns   |                    |

|                                    | 15                   |                   | 10   | 5    | ns   |                    |

| Maximum clock                      | 5                    |                   | 3    | 6    | MHz  | ]                  |

| pulse frequency                    | 10                   | f <sub>max</sub>  | 8    | 16   | MHz  |                    |

|                                    | 15                   |                   | 12   | 24   | MHz  |                    |

|                 | V <sub>DD</sub><br>V | TYPICAL FORMULA FOR P (μW)                 |                                              |

|-----------------|----------------------|--------------------------------------------|----------------------------------------------|

| Dynamic power   | 5                    | 475 $f_i + \sum (f_o CL) \times V_{DD}^2$  | where                                        |

| dissipation per | 10                   | 2400 $f_i + \sum (f_o CL) \times V_{DD}^2$ | f <sub>i</sub> = input freq. (MHz)           |

| package (P)     | 15                   | 6700 $f_i + \sum (f_o CL) \times V_{DD}^2$ | f <sub>o</sub> = output freq. (MHz)          |

|                 |                      |                                            | C <sub>L</sub> = total load capacitance (pF) |

|                 |                      |                                            | $\sum (f_oC_L) = \text{sum of outputs}$      |

|                 |                      |                                            | V <sub>DD</sub> = supply voltage (V)         |

## 4-stage divide-by-8 Johnson counter

HEF4022B MSI

## 4-stage divide-by-8 Johnson counter

HEF4022B MSI

## 4-stage divide-by-8 Johnson counter

HEF4022B MSI

#### **APPLICATION INFORMATION**

Some of the features of the HEF4022B are:

- · High speed

- Spike-free decoded outputs

- · Carry output for cascading

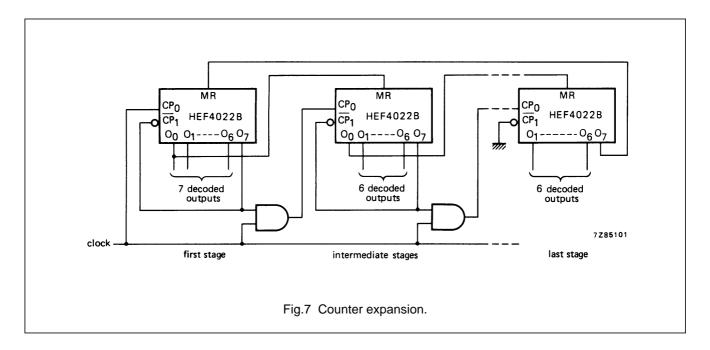

Figure 7 shows a technique for extending the number of decoded output states for the HEF4022B. Decoded outputs are sequential within each stage and from stage to stage, with no dead time (except propagation delay).